International Journal of Advanced Research in Computer and Communication Engineering ISO 3297:2007 Certified

Vol. 7, Issue 4, April 2018

# CMOS based Voltage Reference Generator: A Review

Sneha Meshram<sup>1</sup>, Uday Panwar<sup>2</sup>

Student, Dept. Electronics and Communications, Sagar Institute of Research and Technology, Bhopal, India<sup>1</sup>

Associate Professor, Dept. Electronics and Communications, Sagar Institute of Research and Technology, Bhopal, India<sup>2</sup>

**Abstract:** This paper presents a review of the designs of different voltage reference circuits on the basis of different parameters such as  $V_{ref}$ , supply range, power dissipation, temperature coefficient etc. The circuits reviewed are ultralow power. Recent research in CMOS integrated voltage generators has resulted in the development of components that make possible the design of a high performance linear CMOS voltage reference generators with low output noise. In this paper, few of the designs are reviewed on the basis of the performance of the circuits.

Keywords: Voltage Reference, MOSFET, Current reference.

## INTRODUCTION

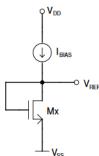

Numerous arrangements exist in writing to produce a reference voltage. A common approach comprises in utilizing a bandgap reference, which can be executed in any standard CMOS innovation misusing the parasitic vertical BJTs [1, 2]. Other voltage references abuse the guideline of edge voltage contrast, which can be founded on a specific channel embed [3, 4], level band voltage distinction got by various entryway materials [5] and work contrast acquired by distinctive entryway doping [6]. Such arrangements cannot be actualized in a standard CMOS innovation since they require extra manufacture steps. An extra sort of voltage reference, executed with a standard CMOS innovation, depends on weighted entryway source voltage distinction between a NMOS and a PMOS transistor [7, 8]. In this paper we examine a voltage reference, which can be executed in any standard CMOS innovation, in light of the weighted door source voltage contrast between two NMOS transistors. Figure 1 shows a basic voltage reference generator using MOS logic.

Figure 1: Voltage Reference Generator

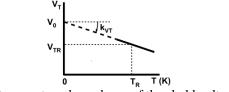

The primary standard for most MOSFET-just voltage references is to predisposition at least one MOSFETs with a present generator with some unequivocal temperature reliance, to create the reference voltage (VREF). The essential topology appeared in Fig. 1 [8]. The present generator gives control supply dismissal. In light of the great linearity of the edge voltage of a MOSFET (VT) as a component of supreme temperature (T), the got reference voltage is much of the time equivalent to V0, the extrapolation of VT (T) to 0 K (Fig. 2), which for the most part decides the base supply voltage. A few plans beat this impediment by utilizing two NMOS transistors with various limit voltages [12]–[14] yet this component isn't accessible in all manufacture innovations. As of late, a reference in light of the distinction in limit voltage in two transistors of a similar sort with various size was proposed in the paper [15].

Figure 2: temperature dependence of threshold voltage Vt

# IJARCCE

#### International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified Vol. 7, Issue 4, April 2018

The temperature reliability of the VTH reference thusly relies upon the temperature reliance of the biasing current. The thought behind voltage references that endeavour the specific zero temperature coefficient biasing point was initially exhibited by Manku et al.[21] utilizing a steady biasing current. A reference circuit in view of this guideline was introduced by Filanovsky et al. [8]. Later Najafizadeh et al. [9] proposed a reference circuit utilizing a biasing current relative to supreme temperature (PTAT), which around makes up for the nonlinear temperature reliance of versatility. De Vita et al. [10] exhibited a voltage reference with full cancelation of the temperature reliance of bearer portability. The proposed current generator required NMOS transistors with two distinctive edge voltages. Rossi et al. [22] additionally summed up the VTH investigation for any reversal level and proposed the utilization of a more straightforward current generator, however that work just exhibited an underlying evidence of idea, as no working usage was displayed. A voltage reference in view of this approach was later actualized without precedent for [23]. That plan requires just a single sort of MOS transistor and consequently it is usable with any procedure.

### LITERATURE REVIEW

A voltage reference is a circuit that gives consistent voltage regardless of temperature or supply voltage varieties. Voltage references are basic parts in numerous electronic frameworks, for example, information converters, control converters, dynamic irregular access recollections, and radio recurrence circuits. Low temperature and power supply affectability without adjustment of the creation procedure are basic prerequisites of a high-exactness voltage reference. In addition, low power utilization necessity is one of the vital outline criteria in all frameworks. The interest for lowcontrol voltage reference with high accuracy is expanding. A voltage (or current) which is corresponding to outright temperature (PTAT) will be added to another voltage (or current) that is integral to supreme temperature (CTAT) to get a reference voltage free of temperature. Various bandgap and non-bandgap voltage references plans have been executed up until this point. It is elusive which configuration is the best. Because of the nonlinear temperature qualities of VEB, high-exactness yield voltage can't be accomplished without high-arrange temperature pay approaches in regular bandgap voltage references [1]. CMOS Voltage References Based on Threshold Voltage Difference are high accuracy voltage references in light of weighted capacity of limit voltages [2](Vtn and Vtp) or weighted contrast between the VGS[3]. Either extra creation steps or nonlinear temperature terms, for example, bearer portability, are incorporated into the reference circuits. The circuits may incorporate resistors, which intensify the invulnerability to substrate clamor coupling. In this manner, high exactness and minimal effort can't be acquired in the meantime. In addition, these plans repay temperature reliance of portability just at reference temperature. BGR portrayed in [4] can be manufactured in standard CMOS innovation without resistors. The BGR here utilizations just transistors one-sided in immersion or cutoff. The transistors one-sided in immersion, for which exact gadget models are typically accessible, improving the outline procedure. Trimming might be required for high accuracy applications. The low power can be effortlessly accomplished with the transistors one-sided in subthreshold area. The plans accomplish a total cancelation of the impacts of temperature reliance of bearer portability for any temperature [5]-[7]. Additionally channel length tweak and body impact are adjusted. In any case, the plan procedure might be entangled by the transistors in subthreshold district, where exact gadget models are not generally accessible and can be incredibly impacted by the varieties of the procedure. A self-one-sided symmetrically-coordinated current voltage mirror(SM CVM) is utilized as a part of the outline [8], which gives incredible line direction. The outline is like that of a traditional sort BGR with the customary current mirror circuit is supplanted with a SM CVM circuit. Resistors are incorporated into the design. A hypothesis is created, states that the shared pay of portability and limit voltage may brings about zero temperature coefficient predisposition focuses (ZTC) of a MOS transistor[9]. At the point when a CMOS innovation demonstrates the nearness of ZTC point, at that point this approach may give another group of voltage reference circuits. A low temperature coefficient voltage reference circuit without incorporating resistors is portrayed in [10]. The circuit is manufactured in standard CMOS innovation. Neither extraordinary gadgets nor subthreshold transistors are required. Resistor less voltage reference circuits can be worthwhile since the circuit will possess lesser zone in the pass on, when contrasted with that of CMOS voltage references including resistors. Also, the resistorless circuits will be insusceptible to substrate commotion coupling. With the assistance of complementation straight temperature terms, a low power non bandgap voltage reference with no resistor is introduced in this paper. Edge voltage and a PTAT voltage shape the fundamental direct temperature parts, which are accomplished by resistorless edge voltage extractor and differential contrast intensifier. Furthermore, a self-one-sided current source is utilized to give stable inclination streams to the entire voltage reference, which can enhance the Power-Supply Commotion Weakening (PSNA).

### CONCLUSION

In this paper, an ultra-low-voltage and ultra-low-control CMOS voltage reference is looked into and examined upon temperature steadiness in light of 0.18-µm CMOS process. The strategy for temperature pay has been portrayed in detail. This circuit does not require the high limit voltage gadget utilizing the body impact method contrast with the structures proposed beforehand. The temperature-remunerated yield reference voltage can be effectively to change and trimming due to the exchanged capacitors method.

# IJARCCE

International Journal of Advanced Research in Computer and Communication Engineering

ISO 3297:2007 Certified

Vol. 7, Issue 4, April 2018

#### REFERENCES

- [1]G. A. Rincón-Mora, Voltage References From Diodes to Precision High-Order Bandgap Circuits, IEEE Press, John Wiley and Sons, Inc., 2002, ISBN: 0471143367.

- [2]B. S. Melody and P. R. Dark, "An exactness bend remunerated CMOS bandgap reference," IEEE J. Strong State Circuits, vol. SC-18, pp. 634– 643, Dec. 1983

- [3]Jiang Y, Lee E K F Design of low-voltage bandgap reference utilizing transimpedance intensifier. IEEE Transaction on Circuits and Systems 11,2000,47(6);552-555

- [4] H. Banba, H. Shiga, A. Umezawa, T. Miyabata, T. Tanzawa, S. Atsumi, and K. Sakuii, "A CMOS bandgap reference circuit with sub-1-V operation,"IEEE J. Strong State Circuits, vol. 34, pp. 670–674, May 1999.

- [5]P. Maloberti, F. Fiocchi, C. Pruzzi, Curvature-remunerated BiCMOS bandgap with 1-V supply voltage. IEEE J. Strong State Circuits, 2001, Vol. 36(7):1076 - 1081

- [6]K. N. Leung and P. K. T. Mok, "A sub-1-V 15 ppm/°C CMOS bandgap voltage reference without requiring low limit voltage gadget," IEEE J. Strong State Circuits, vol. 37, pp. 526-530, Apr. 2002.

[7]G. De Vita and G. Iannaccone, "A Sub-1-V, 10ppm/°C, Nanopower Voltage Reference Generator," IEEE J. Strong State Circuits, pp. 1536-1542,

- [7]G. De Vita and G. Iannaccone, "A Sub-1-V, 10ppm/°C, Nanopower Voltage Reference Generator," IEEE J. Strong State Circuits, pp. 1536-1542, July 2007.

- [8]E. A. Vittoz and J. Fellrath, "CMOS simple incorporated circuits in light of powerless reversal task," IEEE J. Strong State Circuits, vol. SC-12, pp.224–231, June 1977.

- [9]G. Giustolisi, G. Palumbo, M. Criscione, and F. Cutt`ı, "A low voltage low-control voltage reference in light of subthreshold MOSFETs," IEEE J. Strong State Circuits, vol.38, no.1,pp.151–154, Jan.2003.

- [10]B.- S. Melody and P. R. Dim, "Edge voltage temperature float in particle embedded MOS transistors," IEEE J. Strong State Circuits, vol. SC-17, no. 2, pp. 291–298, Apr. 1982.

- [11]Hong-Wei Huang, Chun-Yu Hsieh, Ke-Horng Chen, Sy-Yen Kuo, "A 1V 16.9ppm/°C250nA Switched-Capacitor CMOS Voltage Reference," ISSCC 2008/SESSION 24/ANALOG POWER TECHNIQUES/24.3

- [12]Yean-Kuo Luo, Ke-Horng Chen, Wei-Chou Hsu, "A double stage accuse direct controller of nano-ampere exchanged capacitor CMOS voltage reference for accomplishing low yield swells," the fifteenth IEEE International Conference on Electronics, Circuits and Systems, pp. 446 – 449, Sept. 3 2008